# ON THE SELECTION OF OPTIMAL STRUCTURE ORGANIZATION OF LOGIC MULTICONTROLLERS

#### E.I. Vatutin, V.S. Titov

### Southwest State University, Kursk E-mail: <u>evatutin@rambler.ru</u>

**Abstract.** In the article the basic approaches to structural-parametric optimization of logical control systems (LCS) in the basis of logical multicontrollers (LMC) were given. Based on the results of a series of computational experiments we obtained the set of dependencies on the deterioration of the quality criteria of separations of graph-schemes of parallel logic control algorithms and corresponding parameters values of LMC from technological restrictions on the controller structure. It is shown that the structure of the LMC with a large number of simple controllers is preferred.

**Keywords:** logical control systems, logical multicontrollers, structural-parametric optimization, graph-schemes of parallel algorithms, separations, BOINC.

One of the promising approaches to the synthesis of logic control systems (LCS) is their implementation in the basis of logical multicontroller (LMC) [1-4] which are interconnected in the collective working in parallel similar controllers together solving the problem to implement epy given logic control algorithm presented by corresponding graph-scheme. When designing such multisystems there is a number of discrete combinatorial optimization problems [5]. One of them is the problem of getting suboptimal separation of a priori known graph-scheme of parallel logic control algorithm to sequential blocks with restricted complexity, each of which is implemented by one of the controllers within the LMC. This problem relates to the NP complexity class that does not allow to find the optimal solution for its practical dimension cases (graph-schemes with more than 10–20 vertices) at a reasonable time, therefore its solutions are known and have been successfully used with various heuristic approaches [6-11] having different implementation complexity, asymptotic time and memory complexities of corresponding algorithms, set of optimized partial quality criteria and integral quality of the obtained solutions. The quality of separations directly affects the hardware complexity of the LMC and its speed characteristics.

During LMC design can be used two different approaches. According to the first of them the structure of LMC (number of modules and its hardware characteristics, topology of the connections between them, redundancy options, etc.) is selected once, based on the specific graph-scheme of control algorithm and selected separation for the implementation of which it is necessary to create appropriate LCS. Numerical parameters of separation (number of blocks and links between them) determine the hardware requirements for LMC, and when you change the control algorithm selection LMC structure is actually made anew. This approach can be used, for example, as a way of implementation of control part for specialized computing device with ASIC based production the operating part of which is selected at the design stage and is not changed during further operation. According to the second approach the structure of LMC is generalized and focused on the implementation of one of the group of control algorithms by software setting that makes it possible to change the control algorithm without changing the hardware structure of LMC during operation. This approach can be used, for example, as implementation of assembly line control system in which the set of operations may vary with time. From the standpoint of producer of these LCSs named as programmed logic controllers (PLC) it is interesting to the development of the model range formed by a group of products with different cost and performance characteristics. At the same time design engineer of control part has the opportunity to select one of the LMC models within corresponding model range enough to please it as a cost and the possibility of implementing of the needed control algorithm. Easy to see that the first approach is the analogue of well known ASIC approach that is characterized by rather a high cost while the second one is essentially similar to the practical use of logical circuits with reconfigurable structure such as FPGAs (Field-Programmable Gate Array) and ULAs (Uncommited Logic Array) [12] that can significantly reduce the cost of the final solution for its practical use.

When choosing an appropriate model range a number of issues is arisen connected with structural-parametric optimization of forming its multicontrollers and selecting its structure organization corresponding to practical requirements. For example, when a physical limitation (balance requirements) by the number of transistors, metallization layers on a chip, requirements of electromagnetic and/or thermal compatibility of electronic components and so on you must choose such a structure of LMC that will be characterized by low production costs (for example, with a small area on a chip) and at the same time allows the implementation of a particular group of control algorithms (for example, with selected number of vertices, control signals and speed characteristics) without the need to change the current model of composed model range for more expensive one on the one hand and on the other performance degradation on the another hand. In its simplest form, the need to choose such a structure leads to specifying the number of controllers within the LMC and its hardware performance, while maintaining the given hardware complexity of multisystem within the prescribed limits. In other words, it is possible to implement the LMC, which includes all other things in its structure being equal a large number of relatively simple controllers, a small number of complex controllers or a compromise version. Structural-parametric optimization of LMC can be achieved by finding the number of separations of logic control algorithms, statistical processing of the results and analysis of changes in average quality criteria trends depending on technological restrictions arising in selecting the appropriate structure of LMC.

A formal presentation of the problem of getting separation has the following form. It is required to obtain a separation  $Sep(A^0) = \{A_1, A_2, ..., A_H\}$  of the set of vertices  $A^0$  for source graph-scheme of parallel logic control algorithm  $G^0 = \langle A^0, V^0 \rangle$  satisfying the following conditions:

$$\bigcup_{i=1}^{H} A_{i} = A^{0}, \quad A_{i} \neq \emptyset, \quad A_{i} \cap A_{j} = \emptyset, \quad i, j = \overline{1, H}, \quad i \neq j,

\neg (a_{i} \omega a_{j}) \forall a_{i}, a_{j} \in A_{k}, \quad i \neq j, \quad k = \overline{1, H},$$

$$W(A_{i}) \leq W_{\max}, \quad |X(A_{i})| \leq X_{\max}, \quad |Y(A_{i})| \leq Y_{\max}, \quad i = \overline{1, H},$$

(1)

where  $\omega$  – designation of a binary relation of vertices parallelism [1–4, 13] reflecting a structural restriction of LMC on the prohibition of parallel vertices within blocks of separation,  $W(A_i) = \sum_{a_j \in A_i} W(a_j)$  – summary "weight" of vertices within the *i*-th block (size in controller

memory measured at microcommands);  $X(A_i) = \bigcup_{a_j \in A_i} X(a_j) - a$  set of logical conditions included in the vertices within the *i*-th block;  $Y(A_i) = \bigcup_{a_j \in A_i} Y(a_j) - a$  set of microoperations

included in the vertices within the *i*-th block,  $W_{\text{max}}$  – constraint in the memory capacity of the controller as part of LCS,  $X_{\text{max}}$  – constraint in the number of signals of logic conditions received by the controller,  $Y_{\text{max}}$  – constraint in the number of microoperation signals issued by the controller, such that

$$Z_{H} = H\left(Sep\left(A^{0}\right)\right) \to \min,$$

$$Z_{\alpha} = \sum_{i=1}^{H} \sum_{j=1, j \neq i}^{H} \alpha\left(A_{i}, A_{j}\right) \to \min,$$

$$Z_{\delta} = \delta\left(Sep\left(A^{0}\right)\right) \to \min,$$

$$Z_{X} = \sum_{i=1}^{H} \left|X\left(A_{i}\right)\right| - \left|X\left(A^{0}\right)\right| \to \min,$$

$$Z_{Y} = \sum_{i=1}^{H} \left|Y\left(A_{i}\right)\right| - \left|Y\left(A^{0}\right)\right| \to \min,$$

(2)

where  $Z_H = H(Sep(A^0))$  – the number of blocks in the separation;  $Z_{\alpha}$  – complexity of the interconnect network for separation  $Sep(A^0)$ ;  $\alpha(A_i, A_j)$  – coupling coefficient of blocks pair (it is equal to 1 if the blocks are connected by the control in direction from  $A_i$  to  $A_j$ , which requires an additional command for transfer of control between controllers, and 0 otherwise);  $Z_{\delta} = \delta(Sep(A^0))$  – the total number of interblock interactions (summary interblock traffic);  $Z_x$  – the extent of duplication of logical conditions signals;  $Z_\gamma$  – the extent of duplication of microoperations signals. Minimizing these partial quality criteria can decrease hardware complexity of LCS (criteria  $Z_H$ ,  $Z_X$ ,  $Z_\gamma$ ,  $Z_\alpha$ ) by reducing the required number of controllers, and improve performance of LCS (criterion  $Z_{\delta}$ ) by reducing control traffic and communication subsystem loading.

Number of blocks within the separation provides the number of microprograms and accordingly, the number of controllers within LMC, each of them implements one of them. In the absence of technological restrictions  $(X_{\text{max}} = Y_{\text{max}} = W_{\text{max}} = \infty)$  a number of blocks in separation has low theoretically limit that is provided by the value of the parallelism degree of graph-scheme of parallel algorithm  $\omega_{\text{max}} (A^0)$  [1–4, 14].

For each of the heuristic methods [5–10] set of test examples (graph-schemes of parallel control algorithms) can be selected in which they demonstrate the highest quality of solutions compared with other methods, so the specified type of comparison methods is sufficiently subjective. Therefore, in order to realize the objective of comparing the quality of separations given by different heuristic methods with different using conditions we will carry out a comparison of average values of quality criteria of separations using a generator of graphschemes of algorithms with selected parameters (number of vertices, microoperations and logic conditions signals, probabilities of fragments with different type, etc.) and pseudorandom structure [15] working within program system PAE [16-17]. Using this generator it is possible to obtain samples  $\Lambda = \{G_1^0, G_2^0, ..., G_K^0\}$  of graph-schemes of an arbitrary amount K of control algorithms that in its turn provides the ability of objective comparison quality of separations [18– 23] given by different heuristic methods and track the trends in the partial values of quality criteria when changing the values of technological restrictions  $X_{max}$ ,  $Y_{max}$  and  $W_{max}$  and size of a problem N. For the selected conditions of the computational experiment and this method of getting separations it is possible to determine the partial sample average quality criteria values  $\gamma_x$  and probabilities of getting minimum value of selected partial quality criterion  $\rho_x$ ,  $x \in \{H, X, Y, \alpha, \delta, J\}$ , where J – designation of integral quality criterion of separation  $Sep(A_k^0)$ [3-4]

$$J\left(Sep\left(A_{k}^{0}\right)\right) = \frac{K_{H}}{\omega_{\max}\left(A_{k}^{0}\right)}H + \frac{K_{X}}{\left|X\left(A_{k}^{0}\right)\right|}\left(\sum_{i=1}^{H}\left|X\left(A_{i}\right)\right| - \left|X\left(A_{k}^{0}\right)\right|\right)\right) + \frac{K_{Y}}{\left|Y\left(A_{k}^{0}\right)\right|}\left(\sum_{i=1}^{H}\left|Y\left(A_{i}\right)\right| - \left|Y\left(A_{k}^{0}\right)\right|\right)\right) + \frac{K_{\delta}}{\delta\left(A_{k}^{0}\right)}\delta\left(Sep\left(A_{k}^{0}\right)\right) + \frac{K_{\alpha}}{\omega_{\max}\left(A_{k}^{0}\right)\left(\omega_{\max}\left(A_{k}^{0}\right) - 1\right)}\sum_{i=1}^{H}\sum_{j=1,\ i\neq j}^{H}\alpha\left(A_{i}, A_{j}\right),$$

$$(3)$$

which is a weighted sum of normalized partial quality criteria. Here  $K_H, K_X, K_Y, K_{\alpha}, K_{\delta}$  – weighting coefficients that are selected by experts and reflecting the importance of partial quality criteria;  $\delta(A_k^0)$  – the theoretical maximum intensity of interblock interactions achieved in the separation where each vertex of control algorithm forms a separate block.

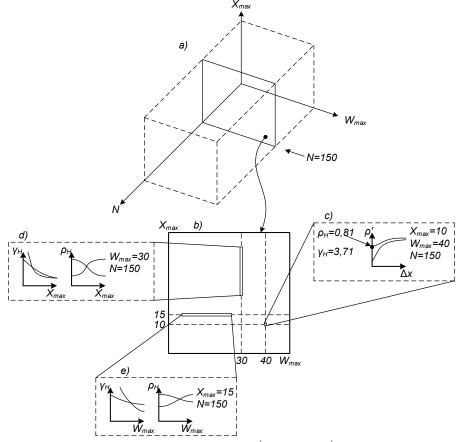

In a series of computational experiments [18–23] that are computationally complex (the amount of computation is required hundreds of years of CPU time [21–23]) and is performed using a grid system on a voluntary basis within volunteer distributed computing project Gerasim@home [24, 25] at BOINC platform [26] it was shown that quality of separations and probabilities of getting best decisions vary significantly for different heuristic methods and for different regions of space (fig. 1) formed by the size of the problem N and values of technological restrictions  $X_{\text{max}}$  and  $W_{\text{max}}$  (restriction  $Y_{\text{max}}$  can be simply avoided by doubling the controller within LMC [1–4]).

Fig. 1. Space of parameters (a), map of the slice  $(X_{max}, W_{max})$  (b) and early one parameter computational experiments (c, d, e)

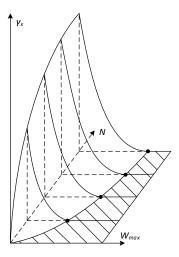

General view of the dependency of partial quality criterion from the dimension of the problem and the value (power) of technological restriction is shown in fig. 2 [27].

Fig. 2. The general behavior of partial quality criteria Z depending on size of the problem N and power of constraint ( $W_{max}$  in this example). Shaded area shows the area of insensitivity

At low values of technological restrictions  $(X_{\max}, W_{\max} \to \infty)$  quality of separation is independent from the technological restrictions and other factors (such as structure restrictions of LMC basis and parameters of source graph-scheme  $G^0$ ). During increasing power of restriction  $(X_{\max}, W_{\max} \to 0)$  values of partial quality criteria begin to increase monotonically. In the area of insensitivity (shown at fig. 2 shaded) changes of partial quality criteria does not occur that allows to optimize structure of LMC by formulating requirements for limiting values  $X'_{\max}$  and  $W'_{\max}$  of technological restrictions for selected size of graph-schemes of logic control N. So when  $(X_{\max} > X'_{\max}) \land (W_{\max} > W'_{\max})$  it is an increase in hardware complexity of controllers and LCS without getting the smaller values of partial quality criteria of partitions that is inappropriate.

In the article [27] as a result of computing experiments boundaries of insensitivity area were obtained. They are based on results of separations, obtained using the method of parallel-sequential decomposition as having minimal values of  $X'_{max}$  and  $W'_{max}$  from all other methods, and allows to formulate the hardware requirements for controllers within LMC with matrix structure (as an example). For example, controllers within matrix LMC with  $7 \times 7 = 49$  modules must have 120 memory cells (command words) for microprogram storing (that corresponds to source graph-scheme of control algorithm separated by blocks) and 86 pins for receiving logic condition signals from controlling object that allows to implement graph-scheme with 450 vertices.

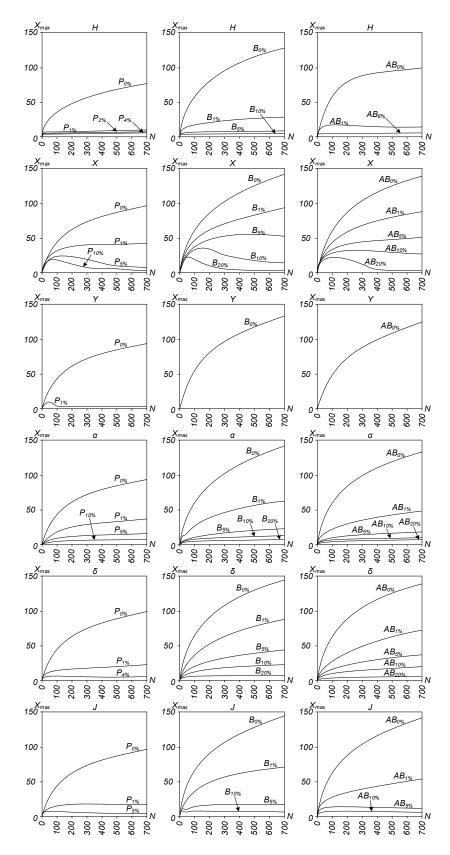

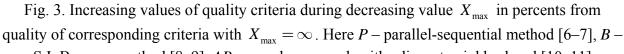

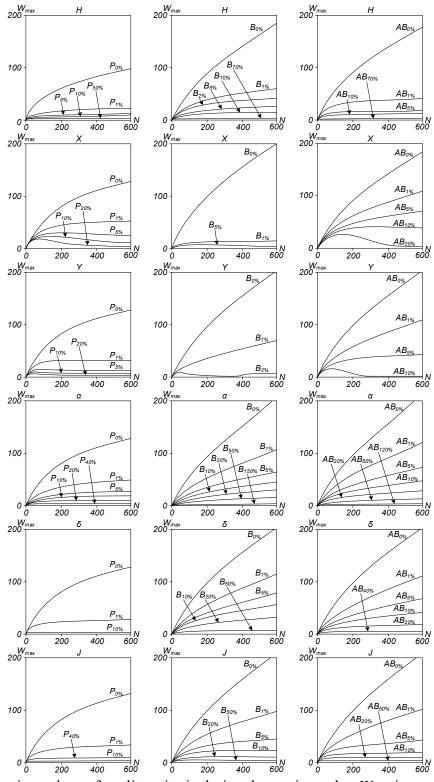

Decreasing values  $X_{\text{max}}$  and  $W_{\text{max}}$  less than the limits (for example, because of the inability or inexpediency production of LMC in the hardware configuration of the technological or cost reasons) leads to growth of partial quality criteria values (see fig. 2) that reduces the speed of the designed LCS due to the increasing control transfer traffic between controllers, increases hardware complexity of communication subsystem of controllers due to the need to implement a greater number of inter-module commands of the control transfer and greater depths of corresponding queues, and also requires the implementation of a larger number of controllers in comparison with a theoretical lower limit  $\omega_{\text{max}} (A^0)$ . This is quite an important study showing how this or that partial quality criteria value deteriorates during increasing power of restrictions (decreasing values  $X_{\text{max}}$  and  $W_{\text{max}}$ ). The answer to this question is obtained while processing the results of a series of computation experiments and shown at fig. 3 and 4, where level lines

marked as  $F_{z\%}$  correspond to decreasing quality of decision by z% comparing to theoretical minimum that provided by method *F* for selected size of a problem *N*. These dependences allow a quantitative study of the characteristics of separations during decreasing values of technological restrictions.

S.I. Baranov method [8–9], AB – greedy approach with adjacent neighborhood [10–11]

Fig. 4. Increasing values of quality criteria during decreasing value  $W_{\text{max}}$  in percents from quality of corresponding criteria with  $W_{\text{max}} = \infty$

An analysis of given results allows to conclude that decreasing quality of decisions for parallel-sequential method in relative units is lower than the same results by S.I. Baranov method and greedy adjacent method. Methods that are based on greedy strategy of building separation shows significantly more deterioration in the quality of decisions on criteria of interblock links number and intensity of interconnect control traffic, especially during reducing the limit value of the controller memory capacity  $W_{\text{max}}$ . As we have noted previously [22, 27], values  $X'_{\text{max}}$  and  $W'_{\text{max}}$  for parallel-sequential method [6–7] are closer to zero (respectively, its insensitivity zone is wider) comparing to variations of greedy approaches [8–11]. This feature allows to recommend the method of series-parallel decomposition to practical use as providing a minimal increase of quality criteria values during decreasing values of technological restrictions.

In practice, it is more important not simply start making deterioration but deterioration in the presence of any predetermined value, empirically selected by the developer of LCS. For example, during performing program optimization of software empirical limit of decreasing time complexity is value of 5% [28] and optimizations providing less decrease are often ignored due to the fact that they are characterized by unpredictable behavior of the speed characteristics of the programs within the time interval measurement error. Assuming deterioration of the integral criterion J within 5% from theoretical limit the technological restrictions can be significantly reduced in comparison with [27], as shown in the table 1.

| quanty chienon                                                                           |                            |                        |               |                             |               |

|------------------------------------------------------------------------------------------|----------------------------|------------------------|---------------|-----------------------------|---------------|

| Number of<br>controllers ( <i>H</i> )<br>within<br>multicontroller<br>without redundancy | Average                    | Limit restrictions     |               | Limit restrictions (allowed |               |

|                                                                                          | number of                  | (without decreasing of |               | 5%-e decreasing of integral |               |

|                                                                                          | vertices (N)               | integral criterion J)  |               | criterion J)                |               |

|                                                                                          | within graph-              |                        |               |                             |               |

|                                                                                          | scheme, no                 | $X'_{ m max}$          | $W'_{ m max}$ | $X'_{ m max}$               | $W'_{ m max}$ |

|                                                                                          | more than                  |                        |               |                             |               |

|                                                                                          | (where                     |                        |               |                             |               |

|                                                                                          | $X_{\max} \ge X'_{\max}$   |                        |               |                             |               |

|                                                                                          | and                        |                        |               |                             |               |

|                                                                                          | $W_{\max} \ge W'_{\max}$ ) |                        |               |                             |               |

| $3 \times 3 = 9$                                                                         | 50                         | 30                     | 34            | 7                           | 13            |

| $4 \times 4 = 16$                                                                        | 110                        | 49                     | 61            | 7                           | 16            |

| $5 \times 5 = 25$                                                                        | 200                        | 64                     | 84            | 6                           | 18            |

| 6×6=36                                                                                   | 312                        | 76                     | 105           | 5                           | 20            |

| $7 \times 7 = 49$                                                                        | 450                        | 86                     | 120           | 5                           | 21            |

| $7 \times 8 = 56$                                                                        | 535                        | 89                     | 126           | 5                           | 21            |

Table 1. Comparison of given limits for zero cases [27] and 5% deterioration of the integral quality criterion

For example, above mentioned configuration of LMC with  $7 \times 7$  controllers limits to a number of received logical condition signals decreased from 86 to 5 pins and limits to volume of memory – from 120 to 21 command words that allows significantly (some times less) decrease the hardware complexity of controllers within LMC and total hardware complexity of LCS at the cost of 5% deterioration in the quality of partial quality criteria (for example, speed characteristics of hardware complexity of communication subsystem).

So as one of results of analysis of computational experiments data, we can conclude that for the implementation of graph-schemes of logic control with a different number of vertices it is preferably using large number of relatively simple controllers within LMC with a small number of pins for receiving logic control signals  $X'_{max}$  and small volume of microprogram memory  $W'_{max}$  that leads to no more than 5% deterioration of the quality of integral quality criterion and, accordingly, technical characteristics of LCS. Increasing complexity of the controller structure leads to the increase in hardware complexity and cost of production for LMCs and does not lead to a significant increase in performance or reduce the number of modules in the LCS and may be considered inappropriate. The number of relatively simple controllers within LMC is relatively large and very similar situation with the presence of a large number of control exchanges between controllers  $Z_{\delta}$  that imposes corresponding requirements on the communications subsystem and makes important subtask of minimizing the intermodule control transfer traffic [1–2]. The shown experimental data (table 3) can serve as a starting point for selecting the preferred LMC structure in the formation of the corresponding model range starting from the specific limits of technological limitations. These restrictions limit values objectively force to work in the field of strong restrictions (close to zero values), where getting the best possible solutions provides a method of parallel-sequential decomposition [18–22] that confirms the expediency of its use in practice in both for design the LCS within LMC basis and during performing of their structural-parametric optimization.

The authors would like to thank all volunteers who took part in the calculation within the distributed computing project Gerasim@Home. The authors also wish to thank Anna Vayzbina for assistance in preparing the English version of the article.

### BIBLIOGRAPHY

1. Zotov I.V., Koloskov V.A., Titov V.S. et al. Organization and Synthesis of Microprogram Multimicrocontrollers (in Russian). Kursk: Kursk State Technical University, 1999. 368 p.

2. Emelyanov S.G., Zotov I.V., Titov V.S. Architecture of parallel logical multicontrollers (in Russian). M: Vishaya shkola, 2009. 233 p.

3. Vatutin E.I., Zotov I.V., Titov V.S. et al. Combinatorial-logic Problems of Synthesis of Separations of Parallel Logic Control Algorithms in Design of Logic Multicontrollers (in Russian). Kursk: Kursk State Technical University, 2010. 200 p.

4. Vatutin E.I. Logic Multicontrollers Design. Getting Separations of Parallel Logic Control Algorithms (in Russian). Saarbrucken: Lambert Academic Publishing, 2011. 292 p.

5. Vatutin E.I., Titov V.S., Emelyanov S.G. Basics of Discrete Combinatorial Optimization. M.: ARGAMAC-MADIA, 2016. 270 p.

6. Vatutin E.I., Zotov I.V. Method for Getting Suboptimal Separations of Parallel Logic Control Algorithms (in Russian) // Parallel Computing and Control Problems (PACO'04). Institute of Control Problems of RAS, Moscow, 2004. p. 884–917.

7. Vatutin E.I., Zotov I.V. Parallel-sequential Method for Getting Separations of Parallel Logic Control Algorithms (in Russian) // Certificate of official registration of the computer software № 2005613091 from 28.11.05.

8. Baranov S.I., Zhuravina L.N., Peschansky V.A. Method for Presentation of Parallel Graphschemes of Algorithms by a Set of Consecutive Graph-schemes (in Russian) // Automatics and Computing. Riga: Institute of Electronics and Computer Science, 1984. p. 74–81.

9. Vatutin E.I. Library of Functions for Getting Separations Using S.I. Baranov Method with Greedy Consecutive Forming of Blocks (in Russian) // Certificate of official registration of the computer software № 2010612902 from 28.04.10.

10. Vatutin E.I., Leonov M.E. Using Adjacent Neighborhood in the Greedy Consecutive Forming of Blocks of Separations of Graph-schemes of Parallel Algorithms (in Russian) // Proceedings of the Higher Educational Institutions. Instrument Making. Vol. 56. № 6. p. 30–35.

11. Vatutin E.I., Titov V.S. Library of functions for getting separations with using adjacent greedy strategy and consecutive forming of blocks (in Russian) // Certificate of official registration of the computer software № 2013619395 from 03.10.13.

12. Ugryumov E.P. Digital circuitry (in Russian). SPb.: BHV-Peterburg, 2004. 528 p.

13. Vatutin E.I., Zotov I.V. Building the Matrix of Relations in the Problem of Getting Separations of Parallel Logic Control Algorithms (in Russian) // Proceedings of Kursk State Technical University. № 2. 2004. p. 85–89.

14. Vatutin E.I. Determining the Parallelism Degree of Graph-scheme of Parallel Algorithm (in Russian) // Intellectual and Informational Systems (Intellect – 2009). Tula State University, 2009. p. 24–26.

15. Vatutin E.I. Constructing Random Sample Parallel Logic Control Algorithms // 11<sup>th</sup> International Student Olympiad on Automatic Control (Baltic Olympiad, BOAC'06). Saint-Petersburg, 2006. p. 162–166.

16. Vatutin E.I., Zotov I.V. Program System for Getting Separations of Parallel Control Algorithms (in Russian) // Systems Identification and Control Problems (SICPRO'06). M.: Institute of Control Problems of RAS, 2006. p. 2239–2250.

17. Vatutin E.I., Zotov I.V. Visual environment for getting separations of parallel logic control algorithms (in Russian) // Certificate of official registration of the computer software  $N_{2}$  2007613222 from 30.07.07.

18. Vatutin E.I., Volobuev S.V., Zotov I.V. A Comprehensive Comparative Evaluation of Methods for Getting Separations During Logic Multicontrollers Design (in Russian) // Systems Identification and Control Problems (SICPRO'08). M.: Institute of Control Problems of RAS, 2008. p. 1917–1940.

19. Vatutin E.I., Volobuev S.V., Zotov I.V. A Comprehensive Comparative Evaluation of Methods for Getting Separations During Logic Multicontrollers Design with Technological Constraints (in Russian) // Parallel Computing and Control Problems (PACO'08). M.: Institute of Control Problems of RAS, 2008. p. 643–685.

20. Vatutin E.I., Titov V.S. Comparison of methods for getting separations of parallel logic control algorithms using two-dimension diagrams (in Russian) // Recognition – 2012. Kursk: Southwest State University, 2012. p. 138–140.

21. Vatutin E.I., Titov V.S. Comparison of methods for the getting separations of the graphschemes of parallel algorithms using two-dimensional diagrams (in Russian) // Proceedings of Southwest State University. No 3 (42), 2012. p. 66–74.

22. Vatutin E.I., Titov V.S. Using distributed volunteer computing systems for analysis of quality of separations of parallel logic control algorithms (in Russian) // Parallel Computing and Control Problems (PACO'12). M.: Institute of Control Problems of RAS, 2012. p. 37–54.

23. Vatutin E.I., Valyaev S.Yu., Titov V.S. Comparison of Sequential Methods for Getting Separations of Parallel Logic Control Algorithms Using Volunteer Computing // CEUR Workshop Proceedings. Vol. 1502. Technical University of Aachen, Germany, 2015. p. 37–51. 24. http://gerasim.boinc.ru

25. Vatutin E.I., Titov V.S. Voluntary distributed computing for solving discrete combinatorial optimization problems using Gerasim@home project // Distributed computing and grid-technologies in science and education: book of abstracts of the 6th international conference. Dubna: JINR, 2014. p. 60–61.

26. http://boinc.berkeley.edu

27. Vatutin E.I., Titov V.S. Structural-parametric optimization of logic control systems using volunteer computing (in Russian) // Proceeding of Southwest State University. Series: Control, Computer Science, Informatics. Medical Devices. № 2. Part 1. 2012. P. 12–17.

28. Kaspersky K. Program optimization technique. Efficient memory usage (in Russian). SPb.: BHV-Peterburg, 2003. 464 p.

# The information about the authors:

Vatutin Eduard Igorevich, Candidate of Technical Sciences, Kursk, Southwest State University, docent of the department "Computing Technics", the sphere of scientific interests - parallel programming, low-level micro-architectural software optimization, getting separations of parallel logic control algorithms during logic multicontrollers design, equivalent transformations and numerical estimations of graph-schemes of parallel algorithms, hardware oriented accelerators and coprocessors design, combinatorial optimization, heuristic methods for discrete combinatorial optimization problems solving, graphs theory, volunteer computing, BOINC.