УДК 681.3

К вопросу о выборе структуры логического

мультиконтроллера

Э.И. Ватутин, канд. техн. наук

Федеральное государственное бюджетное образовательное учреждение

высшего профессионального образования «Юго-Западный государственный

университет», г. Курск

e-mail: evatutin@rambler.ru

В.С. Титов, докт. техн. наук, проф.

Федеральное государственное бюджетное образовательное учреждение

высшего профессионального образования «Юго-Западный государственный

университет», г. Курск

e-mail: titov-swsu@rambler.ru

В подходы статье рассмотрены основные структурно-

параметрической оптимизации систем логического управления (СЛУ) в базисе

логических мультиконтроллеров (ЛМК). С использованием разработанного

генератора граф-схем алгоритмов управления с псевдослучайной структурой

организована серия вычислительных экспериментов, на основании результатов

которой получены зависимости ухудшения частных показателей качества

разбиений граф-схем параллельных алгоритмов логического управления и

соответствующих им параметров ЛМК от значений технологических

ограничений на структуру контроллера. Выявление кривых, ограничивающих

1

область нечувствительности ЛМК к значениям технологических ограничений, позволяет сформулировать предельные требования к аппаратной структуре ЛМК, превышение которых ведет лишь к увеличению аппаратной сложности ЛМК и отдельных контроллеров в его составе и не приводит к улучшению показателей качества функционирования ЛМК (межконтроллерный трафик передачи управления, глубины очередей, степени дублирования сигналов, быстродействие). В статье показано, что при допущении 5%-го ухудшения значений частных показателей функционирования СЛУ возможно существенно (до нескольких раз) снизить аппаратную сложность ЛМК. На основании этого сделан вывод о том, что структура ЛМК с большим числом простых контроллеров является предпочтительной.

Ключевые слова: системы логического управления, логические мультиконтроллеры, структурно-параметрическая оптимизация, граф-схемы параллельных алгоритмов, разбиения, BOINC.

### Введение

Одним из перспективных подходов к синтезу систем логического управления (СЛУ) является ИХ реализация базисе В логических [1-4],мультиконтроллеров (ЛМК) представляющих собой коллектив взаимосвязанных параллельно работающих однотипных контроллеров, в совокупности решающих задачу по реализации заданного параллельного алгоритма логического управления, представленного в виде соответствующей граф-схемы. При проектировании подобных мультисистем возникает ряд задач дискретной комбинаторной оптимизации, одной из которых является задача отыскания субоптимального разбиения априорно известной граф-схемы параллельного алгоритма логического управления на последовательные фрагменты (блоки) ограниченной сложности, каждый из которых впоследствии

реализуется одним из контроллеров в составе ЛМК. Указанная задача относится к классу *NP* [5], что не позволяет произвести отыскание ее оптимального решения для задач практической размерности (граф-схем алгоритмов с числом вершин более 10–20) за приемлемое время, поэтому для ее решения известны и с успехом применяются различные эвристические подходы [6–11], существенно отличающиеся по трудоемкости реализации, асимптотической временной и емкостной сложности, составу оптимизируемых частных показателей качества и интегральному качеству получаемых решений. Качество получаемых разбиений напрямую влияет на аппаратную сложность ЛМК и его быстродействие.

При проектировании ЛМК могут быть использованы два подхода. Согласно первому из них структура ЛМК (число модулей и их аппаратные характеристики, топология связей между ними, параметры избыточности и т.п.) конкретной выбирается однократно исходя ИЗ граф-схемы алгоритма управления, для реализации которого необходимо создание соответствующей СЛУ, и выбранного разбиения. При этом его параметры (число блоков и состав связей между ними) определяют аппаратные требования к ЛМК, а при изменении алгоритма управления выбор структуры ЛМК фактически производится заново. Данный подход может быть использован, например, как способ реализации управляющей специализированного части ДЛЯ вычислительного устройства в заказном исполнении, состав операционной части которого выбран на этапе проектирования и не изменяется в ходе дальнейшей эксплуатации. При втором подходе структура ЛМК делается обобщенной и ориентированной на реализацию одного из группы алгоритмов управления путем программной настройки СЛУ, что делает возможным изменение управляющего алгоритма без изменения аппаратной структуры ЛМК в ходе эксплуатации. Такой подход может применяться, например, при реализации системы управления сборочным конвейером, состав операций

которого может варьироваться со временем. С точки зрения производителя подобных СЛУ, именуемых программируемыми логическими контроллерами, вызывает интерес разработка модельного ряда, образованного группой ЛМК с различной стоимостью и техническими характеристиками. При этом инженерпроектировщик управляющей части имеет возможность выбора одной из моделей ЛМК, входящей в состав соответствующего модельного ряда и устраивающей его как по стоимости, так и по возможности реализации интересующего алгоритма управления. Несложно заметить, что первый подход является аналогом заказного исполнения микросхем и характеризуется достаточно большой стоимостью, в то время как второй по сути схож с использованием на практике схем с логически изменяемой структурой, таких как программируемые логические интегральные схемы или базовые матричные кристаллы [12], что позволяет существенно снизить стоимость конечного решения при его практическом использовании.

При выборе соответствующего модельного ряда возникает ряд вопросов, связанных со структурно-параметрической оптимизацией входящих в него ЛМК и выбора его структуры, соответствующей практическим требованиям. Так, например, при физическом ограничении (балансе требований) на число транзисторов, слоев металлизации кристалле, требованиях на электромагнитной и/или термической совместимости электронных компонентов и пр. необходимо выбрать такую структуру ЛМК, которая будет характеризоваться невысокой себестоимостью производства (например, иметь малую площадь на кристалле) и в то же время обеспечивать возможность реализации определенной группы алгоритмов управления (например, с заданным числом вершин, управляющих сигналов и требуемыми параметрами быстродействия) без необходимости смены текущей модели в составе модельного ряда на более дорогую с одной стороны и производительности с другой. В простейшем виде необходимость выбора подобной структуры приводит к указаниию числа контроллеров в составе ЛМК и их аппаратных характеристик при сохранении заданной аппаратной сложности мультисистемы в целом в заданных пределах. Другими словами, возможна реализация ЛМК, включающего в своем составе при прочих равных большое число относительно простых контроллеров, малое число сложных либо некий компромиссный вариант. Структурно-параметрическая оптимизация ЛМК может быть осуществлена путем отыскания разбиений ряда алгоритмов логического управления, статистической обработки полученных результатов и анализа тенденций изменения усредненных показателей качества в зависимости от технологических ограничений, возникающих при выборе соответствующей структуры ЛМК.

# Математическая постановка задачи выбора разбиения и оценка его качества

Формализованная постановка задачи поиска разбиения граф-схемы параллельного алгоритма логического управления формулируется следующим образом: требуется получить разбиение  $Sep\left(A^{0}\right) = \left\{A_{1}, A_{2}, ..., A_{H}\right\}$  множества вершин  $A^{0}$ ,  $\left|A^{0}\right| = N$ , граф-схемы исходного управляющего алгоритма  $G^{0} = \left\langle A^{0}, V^{0} \right\rangle$ , удовлетворяющее следующим условиям:

$$\bigcup_{i=1}^{H} A_{i} = A^{0}, \quad A_{i} \neq \emptyset, \quad A_{i} \cap A_{j} = \emptyset, \quad i, j = \overline{1, H}, \quad i \neq j,$$

$$\neg \left(a_{i} \omega a_{j}\right) \forall a_{i}, a_{j} \in A_{k}, \quad i \neq j, \quad k = \overline{1, H},$$

$$W\left(A_{i}\right) \leq W_{\text{max}}, \quad \left|X\left(A_{i}\right)\right| \leq X_{\text{max}}, \quad \left|Y\left(A_{i}\right)\right| \leq Y_{\text{max}}, \quad i = \overline{1, H},$$

(1)

где  $\omega$  – обозначение бинарного отношения параллельности вершин [1–4, 13], отражающее структурное ограничение ЛМК на отсутствие параллельных вершин в составе блоков разбиения;  $W(A_i) = \sum_{a_j \in A_i} W(a_j)$  – суммарный «вес»

вершин в составе і-го блока (необходимая емкость памяти микропрограмм

контроллера в составе СЛУ);  $X(A_i) = \bigcup_{a_j \in A_i} X(a_j)$  — множество логических условий, входящих в вершины i-го блока (число дорожек на прием контроллером сигналов логического управления);  $Y(A_i) = \bigcup_{a_j \in A_i} Y(a_j)$  — множество микроопераций, входящих в вершины i-го блока (число дорожек на выдачу контроллером сигналов микроопераций);  $W_{\max}$ ,  $X_{\max}$  и  $Y_{\max}$  — технологические ограничения ЛМК соответственно на максимальную емкость памяти микропрограмм контроллеров в составе СЛУ, максимальное число принимаемых контроллером сигналов логических условий от объекта управления и максимальное число выдаваемых контроллером сигналов микроопераций для объекта управления, такое что

$$\begin{split} Z_{H} &= H\left(Sep\left(A^{0}\right)\right) \rightarrow \min\,,\\ Z_{\alpha} &= \sum_{i=1}^{H} \sum_{j=1, j \neq i}^{H} \alpha\left(A_{i}, A_{j}\right) \rightarrow \min\,,\\ Z_{\delta} &= \delta\left(Sep\left(A^{0}\right)\right) \rightarrow \min\,,\\ Z_{X} &= \sum_{i=1}^{H} \left|X\left(A_{i}\right)\right| - \left|X\left(A^{0}\right)\right| \rightarrow \min\,,\\ Z_{Y} &= \sum_{i=1}^{H} \left|Y\left(A_{i}\right)\right| - \left|Y\left(A^{0}\right)\right| \rightarrow \min\,, \end{split}$$

где  $Z_H, Z_X, Z_Y, Z_\alpha, Z_\delta$  — частные показатели качества разбиения:  $Z_H$  — число блоков в разбиении;  $Z_\alpha$  — сложность сети межблочных связей, порождаемая разбиением  $Sep\left(A^0\right)$ ;  $\alpha\left(A_i,A_j\right)$  — коэффициент связи блоков (он равен 1, если блоки разбиения связаны по управлению в направлении от  $A_i$  к  $A_j$ , т.е. необходима команда межконтроллерной передачи управления, и 0 в противном случае);  $Z_\delta$  — суммарное число (интенсивность) межблочных взаимодействий;

$Z_{\scriptscriptstyle X}$  — степень дублирования сигналов логических условий;  $Z_{\scriptscriptstyle Y}$  — степень дублирования сигналов микроопераций.

блоков в разбиении определяет число микропрограмм соответственно, число контроллеров в составе ЛМК, каждый из которых реализует одну из них. При отсутствующих технологических ограничениях  $\left(X_{\max} = Y_{\max} = W_{\max} = \infty\right)$  число блоков в разбиении теоретически ограничено снизу значением степени параллелизма граф-схемы алгоритма управления  $\omega_{\max} \left(A^0\right)$  [1–4]. Степени дублирования микроопераций и логических условий фактически представляют собой число «лишних» дорожек на кристалле или печатной плате, которые требуется реализовать из-за необходимости передачи соответствующих сигналов к/от контроллерам в составе ЛМК (в предельном случае при группировке вершин со сходными составами микроопераций и логических условий в составе одного блока разбиения данные степени дублирования равны нулю). Число команд межмодульной передачи влияет на разрядность полей соответствующих управления напрямую сообщений и необходимые глубины очередей, т.е. определяет аппаратную сложность коммуникационной части контроллера составе ЛМК. межблочных взаимодействий Интенсивность определяет параметры быстродействия мультисистемы в целом при выполнении заданного алгоритма логического управления, с ее ростом время выдачи сигналов микроопераций определяется не быстродействием контроллера, а временем межмодульных обменов, что накладывает дополнительные ограничения на структурнофункциональную организацию коммуникационной подсистемы ЛМК.

Для каждого из эвристических методов [6–11] возможен выбор тестовых примеров (граф-схем алгоритмов управления), на которых они демонстрирует наивысшее качество решений по сравнению с другими методами, однако указанный тип сравнения методов является в достаточной степени

субъективным. Поэтому с целью реализации объективного сравнения качества разбиений, полученных различными эвристическими методами в различных условиях использования, будем производить сравнение усредненных значений показателей качества разбиений с использованием генератора граф-схем алгоритмов с заданными параметрами (число вершин, число микроопераций и логических условий, вероятности встречаемости фрагментов различного типа и пр.) и псевдослучайной структурой [14], работающего в составе программной системы РАЕ [15-16], на базе которого возможно получение выборок  $\Lambda = \left\{ G_1^0 \,,\, G_2^0 \,,\, ...,\, G_K^0 \right\}$  граф-схем алгоритмов управления произвольного объема К. С помощью данных выборок возможно произвести объективное сравнение качества разбиений [17-22],получаемых различными эвристическими методами, а также проследить тенденции изменения значений частных показателей качества при изменении значений технологических ограничений  $X_{\mathrm{max}}$ ,  $Y_{\mathrm{max}}$  и  $W_{\mathrm{max}}$  и размерности задачи N. Для выбранных условий проведения вычислительного эксперимента и указанного метода синтеза разбиений возможно определение средневыборочных значений частных показателей качества  $\gamma_x$  и вероятностей получения минимального значения выбранного частного показателя качества  $\rho_x$ ,  $x \in \{H, X, Y, \alpha, \delta, J\}$ , где J – обозначение интегрального показателя качества разбиения  $Sep(A_k^0)$  [3–4]

$$J(Sep(A_{k}^{0})) = \frac{K_{H}}{\omega_{\max}(A_{k}^{0})} H + \frac{K_{X}}{|X(A_{k}^{0})|} \left( \sum_{i=1}^{H} |X(A_{i})| - |X(A_{k}^{0})| \right) + \frac{K_{Y}}{|Y(A_{k}^{0})|} \left( \sum_{i=1}^{H} |Y(A_{i})| - |Y(A_{k}^{0})| \right) + \frac{K_{\delta}}{\delta(A_{k}^{0})} \delta(Sep(A_{k}^{0})) + \frac{K_{\alpha}}{\omega_{\max}(A_{k}^{0})(\omega_{\max}(A_{k}^{0}) - 1)} \sum_{i=1}^{H} \sum_{j=1, i \neq j}^{H} \alpha(A_{i}, A_{j}),$$

$$(3)$$

представляющего собой взвешенную сумму нормированных значений частных показателей качества. Здесь  $K_H$ ,  $K_X$ ,  $K_Y$ ,  $K_\alpha$ ,  $K_\delta$  — весовые коэффициенты, выбираемые экспертным путем и отражающие значимость частных показателей качества;  $\delta \left( A_k^0 \right)$  — максимально возможная интенсивность межблочных взаимодействий, достигаемая в случае разбиения, в котором каждая вершина граф-схемы алгоритма управления образует собой отдельный блок разбиения.

# Анализ тенденций изменения качества разбиений при изменении значений технологических ограничений

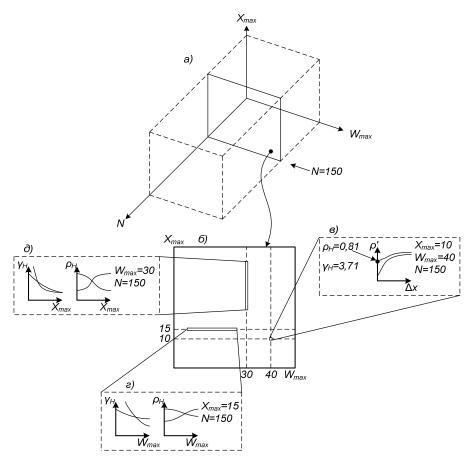

В ходе ряда вычислительных экспериментов [17-22], являющихся вычислительно сложными (необходимый объем вычислений составляет сотни лет процессорного времени [20-22]) и выполненных с использованием гридсистем на добровольной основе В рамках проекта добровольных распределенных вычислений Gerasim@home [23–24] на платформе BOINC [25], было показано, что качество разбиений и вероятность отыскания лучших решений существенно варьируются как для различных эвристических методов, так и для различных областей пространства (рис. 1), образованного значениями задачи N и технологических ограничений  $X_{\max}$  и размерности (ограничение  $Y_{\max}$  исключено из рассмотрения, т.к. оно легко обходится путем дублирования контроллера в составе ЛМК [1-4]).

Рис. 1. Пространство параметров (а), карта в разрезе параметров  $\left(X_{\max},W_{\max}\right)$  (б) и различные вычислительные эксперименты (в, г, д)

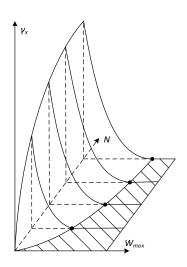

Общий вид зависимостей частных показателей качества от размерности задачи и значения технологического ограничения [26] приведен на рис. 2.

Рис. 2. Общий вид зависимостей частных показателей качества от размерности задачи и значения технологического ограничения. Штриховкой показана т.н. область нечувствительности

При слабом значении технологического ограничения  $(X_{\max}, W_{\max} \to \infty)$  качество разбиения не зависит от значения ограничения и определяется другими факторами (структурными ограничениями базиса ЛМК и параметрами граф-схемы алгоритма управления  $G^0$ ), однако по мере его усиления  $(X_{\max}, W_{\max} \to 0)$  значения частных показателей начинают монотонно возрастать. В области нечувствительности, показанной на рис. 2 штриховкой, изменения частных показателей качества разбиений не происходит, что с точки зрения оптимизации структуры ЛМК позволяет сформулировать ограничения на предельные значения  $X'_{\max}$  и  $W'_{\max}$  технологических ограничений для выбранной размерности граф-схем алгоритмов логического управления N. Так при  $(X_{\max} > X'_{\max}) \wedge (W_{\max} > W'_{\max})$  происходит увеличение аппаратной сложности контроллеров и СЛУ в целом без получения меньших значений частных показателей качества разбиений, что нецелесообразно.

В работе [26] в ходе анализа экспериментальных данных были получены границы области нечувствительности и, отталкиваясь от разбиений,

получаемых с применением метода параллельно-последовательной декомпозиции, имеющего среди остальных эвристических методов наименьшие значения  $X'_{\max}$  и  $W'_{\max}$ , что позволяет сформулировать аппаратные требования к контроллерам в составе ЛМК с матричной структурой. Так, например, контроллеры в составе матричного ЛМК из  $7 \times 7 = 49$  модулей должны иметь в своем составе по 120 ячеек памяти (слов) для хранения микрокоманд, соответствующих вершинам граф-схемы, и 86 выводов для приема сигналов логических условий от объекта управления, что позволяет им реализацию графсхем алгоритмов логического управления в среднем из 450 вершин.

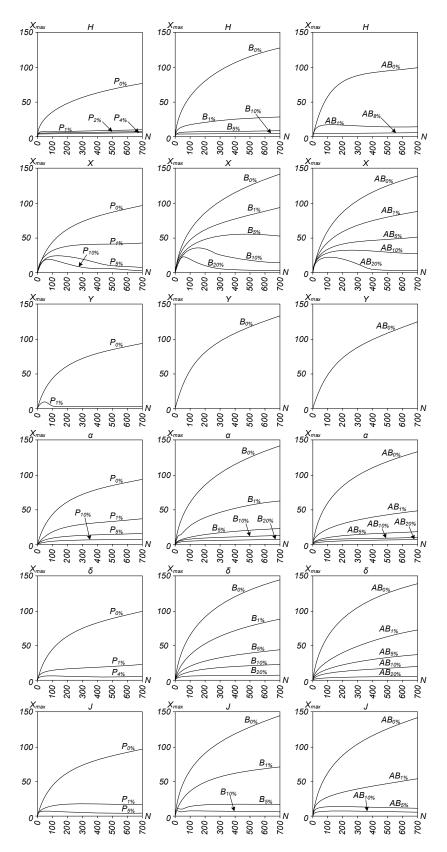

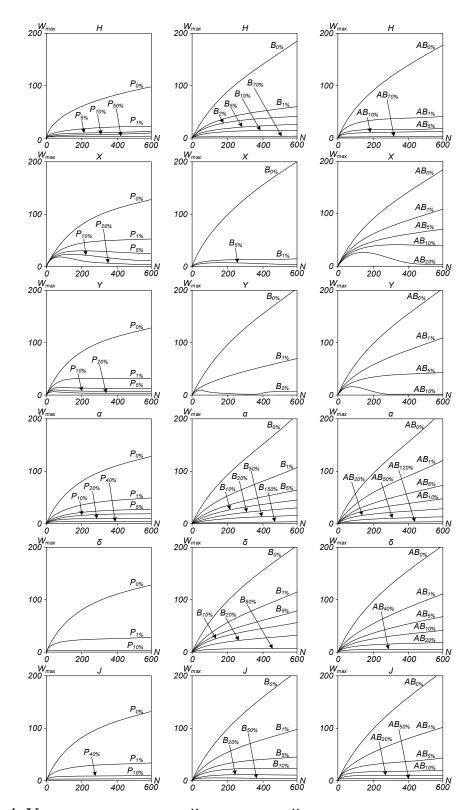

При уменьшении значений  $X_{\mathrm{max}}$  и  $W_{\mathrm{max}}$  меньше предельных (например, из-за невозможности или нецелесообразности изготовления ЛМК в данной аппаратной конфигурации по технологическим или стоимостным причинам) наблюдается рост частных показателей разбиений (см. рис. 2), что снижает быстродействие проектируемой СЛУ из-за возрастающего межконтроллерного трафика передачи управления, повышает аппаратную сложность коммуникационной контроллеров необходимости подсистемы ввиду реализации большего числа команд межмодульной передачи управления и больших глубин соответствующих очередей в их составе, а также требует реализации большего числа контроллеров в составе ЛМК по сравнению с теоретическим нижним пределом  $\omega_{\max} \left( A^0 \right)$ . При этом достаточно важным является исследование того, насколько ухудшается тот или иной частный показатель по мере увеличения силы ограничений (уменьшения значений  $X_{\rm max}$ и  $W_{\mathrm{max}}$ ). Ответ на данный вопрос, полученный в ходе обработки результатов серии вычислительных экспериментов, приведен на рис. 3-4, где линии уровня, помеченные как  $F_{z\%}$ , соответствуют ухудшению решения на z% по сравнению теоретическим минимумом, полученным методом F при заданной размерности задачи N (числа вершин в составе граф-схемы алгоритма

управления  $G^0$ ). Приведенные зависимости дают возможность количественного изучения характеристик разбиений по мере уменьшения значений технологических ограничений. Максимальные ухудшения усредненных показателей качества приведены в табл. 1 и 2.

Анализ полученных данных позволяет сделать вывод о том, что ухудшение качества решений для параллельно-последовательного метода в относительных единицах меньше, чем для методов С.И. Баранова и метода, основанного на жадной смежной стратегии, для большинства показателей качества (за исключением показателя  $\gamma_v$ ). При этом методы, основанные на жадном формировании блоков разбиения, испытывают существенно большее ухудшение качества решений по критериям числа межблочных связей и интенсивности межблочных взаимодействий, в особенности при уменьшении значения ограничения на емкость памяти контроллера  $W_{\max}$ . Как уже было отмечено ранее [22, 26], значения  $X'_{\max}$  и  $W'_{\max}$  для метода параллельнопоследовательной декомпозиции [6–7] расположены ближе нулю (соответственно его зона нечувствительности шире), чем для методов, базирующихся на жадной стратегии поблочного формирования разбиения [8-11]. параллельно-Данное свойство позволяет рекомендовать метод последовательной декомпозиции К практическому использованию как обеспечивающий минимальное увеличение значений показателей качества разбиений по мере уменьшения значений технологических ограничений.

Рис. 3. Увеличение значений показателей качества разбиений по мере уменьшения значения  $X_{\rm max}$  в процентах по отношению к значению

соответствующего показателя качества при  $X_{\rm max}=\infty$  . P — метод параллельно-последовательной декомпозиции [6–7], B — метод С.И. Баранова [8–9], AB — жадный подход с ограничением на смежность [10–11]

Рис. 4. Увеличение значений показателей качества по мере уменьшения значения  $W_{\max}$  в процентах по отношению к значению соответствующего показателя качества при  $W_{\max} = \infty$

Таблица 1. Максимальное ухудшение выбранного усредненного показателя качества по мере уменьшения значения ограничения  $X_{\max}$  в процентах по отношению к значению соответствующего показателя качества при  $X_{\max} = \infty$

| Показатель                      | Метод синтеза |     |     |  |  |

|---------------------------------|---------------|-----|-----|--|--|

| качества                        | разбиений     |     |     |  |  |

|                                 | P             | В   | AB  |  |  |

| $\gamma_H$                      | 4%            | 10% | 8%  |  |  |

| $\gamma_X$                      | 10%           | 20% | 20% |  |  |

| $\gamma_{\scriptscriptstyle Y}$ | 1%            | <1% | <1% |  |  |

| $\gamma_{\alpha}$               | 10%           | 20% | 20% |  |  |

| $\gamma_{\delta}$               | 4%            | 20% | 20% |  |  |

| $\gamma_J$                      | 5%            | 10% | 10% |  |  |

Таблица 2. Максимальное ухудшение выбранного показателя качества по мере уменьшения значения ограничения  $W_{\max}$  в процентах по отношению к значению соответствующего показателя качества при  $W_{\max} = \infty$

| Показатель        | Метод синтеза<br>разбиений |      |      |  |

|-------------------|----------------------------|------|------|--|

| качества          | P                          | В    | AB   |  |

| $\gamma_H$        | 50%                        | 70%  | 70%  |  |

| $\gamma_X$        | 20%                        | 5%   | 20%  |  |

| $\gamma_Y$        | 20%                        | 2%   | 10%  |  |

| $\gamma_{\alpha}$ | 40%                        | 150% | 120% |  |

| $\gamma_{\delta}$ | 10%                        | 50%  | 40%  |  |

| $\gamma_J$ | 40% | 50% | 50% |

|------------|-----|-----|-----|

|            |     |     |     |

На практике зачастую является более важным не просто факт начала ухудшения качества решений, а наличие ухудшения на какую-либо наперед заданную величину, выбираемую проектировщиком эмпирически. например, при проведении оптимизации программного обеспечения эмпирическим пределом является значение 5% [27], а оптимизации, дающие меньший прирост производительности, обычно не рассматриваются, т.к. для зачастую характерно непредсказуемое поведение них скоростных характеристик программ в пределах погрешности измерений временных интервалов. При допущении ухудшения интегрального показателя J в пределах 5% требования К предельным технологическим ограничениям ОНЖОМ существенно снизить по сравнению с [26], что показано в табл. 3.

Таблица 3. Сравнение предельных ограничений для случаев нулевого [26] и пятипроцентного ухудшения интегрального показателя качества

|                    | Среднее                  | Предельные ограничения (без $(N)$ ухудшения интегрального показателя $J$ ) |               | Предельные                       |               |

|--------------------|--------------------------|----------------------------------------------------------------------------|---------------|----------------------------------|---------------|

|                    | число                    |                                                                            |               | (без страничения (допустимо 5%-е |               |

|                    | вершин $(N)$             |                                                                            |               |                                  |               |

| Число              | реализуемой              |                                                                            |               | ухуді                            | пение         |

| контроллеров (Н) в | граф-схемы               |                                                                            |               | интегрального                    |               |

| составе            | алгоритма,               |                                                                            |               | показателя $J$ )                 |               |

| мультиконтроллера  | не более                 |                                                                            |               |                                  |               |

| без учета          | (при                     |                                                                            |               |                                  |               |

| избыточности       | ` 1                      | V'                                                                         | 147/          | X'                               | 147/          |

|                    | условии                  | $X'_{\mathrm{max}}$                                                        | $W'_{ m max}$ | $A_{\text{max}}$                 | $W_{ m max}'$ |

|                    | $X_{\max} \ge X'_{\max}$ |                                                                            |               |                                  |               |

|                    | И                        |                                                                            |               |                                  |               |

|                   | $W_{\max} \ge W'_{\max}$ ) |    |     |   |    |

|-------------------|----------------------------|----|-----|---|----|

| $3\times3=9$      | 50                         | 30 | 34  | 7 | 13 |

| $4\times4=16$     | 110                        | 49 | 61  | 7 | 16 |

| $5 \times 5 = 25$ | 200                        | 64 | 84  | 6 | 18 |

| $6\times 6=36$    | 312                        | 76 | 105 | 5 | 20 |

| $7 \times 7 = 49$ | 450                        | 86 | 120 | 5 | 21 |

| $7\times8=56$     | 535                        | 89 | 126 | 5 | 21 |

Так, например, для упомянутой выше конфигурации ЛМК  $7 \times 7$  контроллеров требования к числу принимаемых сигналов логических условий сокращается с 86 до 5, а требования к объему памяти контроллера — со 120 до 21 слова, что позволяет существенно (в несколько раз) снизить аппаратную сложность контроллеров в составе ЛМК и аппаратную сложность СЛУ в целом ценой 5%-го ухудшения частных показателей качества (например, быстродействия или аппаратной сложности коммуникационной подсистемы).

## Выводы и рекомендации

В ходе анализа приведенных выше данных вычислительных экспериментов можно сделать вывод о том, что для реализации граф-схем параллельных алгоритмов с различным числом вершин предпочтительно использование в составе ЛМК достаточно простых контроллеров с малым числом выводов для приема сигналов логических условий  $X'_{\max}$  и малым объемом памяти микрокоманд  $W_{\mathrm{max}}'$ , что приводит к не более чем 5% ухудшению интегрального качества разбиений и, соответственно, технических характеристик СЛУ. Усложнение же структуры контроллеров приводит к росту аппаратной сложности и себестоимости производства ЛМК, что не приводит к значительному повышению быстродействия или снижению числа модулей в составе СЛУ и может считаться нецелесообразным. При этом число

относительно простых контроллеров в составе ЛМК относительно велико и весьма вероятна ситуация с наличием большого числа межконтроллерных требования обменов  $Z_{\delta}$ , что накладывает соответствующие на коммуникационную подсистему и делает важной подзадачу минимизации трафика передачи управления [1–2]. межконтроллерного Приведенные экспериментальные данные (табл. 3) могут послужить отправной точкой для ЛМК выбора предпочтительной структуры при формировании соответствующего модельного ряда отталкиваясь от конкретных предельных значений технологических ограничений. Полученные значения предельных ограничений объективно вынуждают работать в области сильных ограничений, где получение решений наилучшего качества обеспечивает метод параллельнопоследовательной декомпозиции [16–21], что подтверждает целесообразность его использования на практике как при проектировании СЛУ в базисе ЛМК, так и при выполнении их структурно-параметрической оптимизации.

Работа выполнена в рамках выполнения государственного задания для Юго-Западного государственного университета на 2014–2017 гг., номер НИР 2246, а также гранта Президента РФ МК-9445.2016.8.

### СПИСОК ЛИТЕРАТУРЫ

- 1. Организация и синтез микропрограммных мультимикроконтроллеров / Зотов И.В., Колосков В.А., Титов В.С. и др. Курск: изд-во Курск, 1999. 368 с.

- 2. Архитектура параллельных логических мультиконтроллеров / **Емельянов С.Г., Зотов И.В., Титов В.С.** М: Высшая школа, 2009. 233 с.

- 3. Комбинаторно-логические задачи синтеза разбиений параллельных алгоритмов логического управления при проектировании логических

- мультиконтроллеров / Э.И. Ватутин, И.В. Зотов, В.С. Титов и др. Курск: издво КурскГТУ, 2010. 200 с.

- 4. **Ватутин** Э.И. Проектирование логических мультиконтроллеров. Синтез разбиений параллельных граф-схем алгоритмов. Saarbrücken: Lambert Academic Publishing, 2011. 292 с.

- 5. **Ватутин Э.И., Титов В.С., Емельянов С.Г.** Основы дискретной комбинаторной оптимизации. М.: АРГАМАК-МЕДИА, 2016. 270 с.

- 6. **Ватутин Э.И., Зотов И.В.** Метод формирования субоптимальных разбиений параллельных управляющих алгоритмов // Параллельные вычисления и задачи управления (РАСО'04). М.: ИПУ РАН, 2004. С. 884–917.

- 7. **Ватутин Э.И., Зотов И.В.** Параллельно-последовательный метод формирования субоптимальных разбиений параллельных управляющих алгоритмов // Свидетельство об официальной регистрации программы для ЭВМ № 2005613091 от 28.11.05.

- 8. **Баранов С.И., Журавина Л.Н., Песчанский В.А.** Обобщенный метод декомпозиции граф-схем алгоритмов // А и ВТ. 1982. № 5. С. 43–51.

- 9. **Ватутин Э.И.** Библиотека функций построения разбиений методом С.И. Баранова с жадным последовательным формированием блоков // Свидетельство о государственной регистрации программы для ЭВМ № 2010612902 от 28.04.10.

- 10. **Ватутин Э.И., Леонов М.Е.** Использование смежной окрестности при жадном последовательном формировании блоков разбиения граф-схем параллельных алгоритмов // Известия высших учебных заведений. Приборостроение. 2013. Т. 56. № 6. С. 30–35.

- 11. **Ватутин Э.И., Титов В.С.** Библиотека функций для построения разбиений с использованием смежной жадной стратегии и последовательным формированием блоков // Свидетельство о государственной регистрации программы для ЭВМ № 2013619395 от 03.10.13.

- 12. **Угрюмов Е.П.** Цифровая схемотехника. СПб.: БХВ-Петербург, 2004. 528 с.

- 13. **Ватутин Э.И., Зотов И.В.** Построение матрицы отношений в задаче оптимального разбиения параллельных управляющих алгоритмов // Известия Курского государственного технического университета. Курск, 2004. № 2. С. 85–89.

- 14. **Vatutin E.I.** Constructing Random Sample Parallel Logic Control Algorithms // 11th International Student Olympiad on Automatic Control (Baltic Olympiad, BOAC'06). Saint-Petersburg, 2006. PP. 162–166.

- 15. **Ватутин Э.И., Зотов И.В.** Визуальная среда синтеза разбиений параллельных алгоритмов логического управления // Свидетельство об официальной регистрации программы для ЭВМ № 2007613222 от 30.07.07.

- 16. **Ватутин Э.И., Зотов И.В.** Программная система для построения разбиений параллельных управляющих алгоритмов // Идентификация систем и задачи управления (SICPRO'06). М.: Институт проблем управления им. В.А. Трапезникова РАН, 2006. С. 2239–2250.

- 17. **Ватутин Э.И., Волобуев С.В., Зотов И.В.** Комплексная сравнительная оценка методов выбора разбиений при проектировании логических мультиконтроллеров // Идентификация систем и задачи управления (SICPRO'08). М.: ИПУ РАН, 2008. С. 1917–1940.

- Волобуев С.В., И.В. 18. Ватутин Э.И., Зотов Комплексный сравнительный анализ качества разбиений при синтезе логических мультиконтроллеров в условиях присутствия технологических ограничений // Параллельные вычисления и задачи управления (РАСО'08). М.: ИПУ РАН, 2008. C. 643–685.

- 19. **Ватутин Э.И., Зотов И.В.** Анализ качества блочных разбиений при синтезе логических мультиконтроллеров // Информационно-измерительные и управляющие системы. № 10, Т. 6. М.: «Радиотехника», 2008. С. 32–38.

- 20. **Ватутин Э.И., Титов В.С.** Сравнение методов синтеза разбиений параллельных алгоритмов логического управления с использованием двухпараметрических диаграмм // Оптико-электронные приборы и устройства в системах распознавания образов, обработки изображений и символьной информации (Распознавание 2012). Курск: изд-во ЮЗГУ, 2012. С. 138–140.

- 21. **Ватутин Э.И., Титов В.С.** Сравнение методов синтеза разбиений граф-схем параллельных алгоритмов с использованием двумерных диаграмм // Известия Юго-Западного государственного университета. Курск: изд-во ЮЗГУ, 2012. № 3 (42), 2012. С. 66–74.

- 22. **Ватутин Э.И., Титов В.С.** Использование добровольных распределенных вычислений на платформе BOINC для анализа качества разбиений граф-схем параллельных алгоритмов // Параллельные вычисления и задачи управления (PACO'12). М.: ИПУ РАН, 2012. Т. 2. С. 37–54.

- 23. http://gerasim.boinc.ru

- 24. **Vatutin E.I., Titov V.S.** Voluntary distributed computing for solving discrete combinatorial optimization problems using Gerasim@home project // Distributed computing and grid-technologies in science and education: book of abstracts of the 6th international conference. Dubna: JINR, 2014. PP. 60–61.

- 25. http://boinc.berkeley.edu

- 26. **Ватутин** Э.И., Титов В.С. Структурно-параметрическая оптимизация систем логического управления с использованием добровольных распределенных вычислений // Известия Юго-Западного государственного университета. Серия: Управление, вычислительная техника, информатика. Медицинское приборостроение. 2012. № 2. Ч. 1. С. 12–17.

- 27. **Касперски К.** Техника оптимизации программ. Эффективное использование памяти. СПб: БХВ-Петербург, 2003 г. 464 с.