Ватутин Э.И., Титов В.С. Юго-Западный государственный университет 305040, г. Курск, ул. 50 лет Октября, 94

## Оценка аппаратной сложности логических мультиконтроллеров в зависимости от значений технологических ограничений и методов синтеза разбиений граф-схем параллельных алгоритмов

Одним из распространенных классов цифровых управляющих систем являются логические мультиконтроллеры (ЛМК) [1]. ЛМК представляет собой коллектив однотипных контроллеров, в совокупности решающий возложенную на них задачу управления некоторым объектом путем получения от него сигналов логических условий и выдачи сигналов микроопераций в дискретные моменты времени. В основе проектирования ЛМК лежит задача поиска субоптимального разбиения заданной граф-схемы  $G = \langle A, V \rangle$  параллельного алгоритма логического управления на блоки (подалгоритмы)  $\Gamma = \{A_1, A_2, ..., A_H\}$  ограниченной сложности с целью выполнения каждого из них одним из контроллеров в составе ЛМК. Данная задача относится к дискретным комбинаторным задачам многокритериальной оптимизации, а качество ее решения напрямую влияет на аппаратную сложность и быстродействие синтезируемого ЛМК.

Аппаратная сложность ЛМК складывается из аппаратной сложности логических контроллеров и связывающей их коммуникационной подсистемы и определяется как

$$R = (R_H + R_X X_{\text{max}} + R_Y Y_{\text{max}} + R_W W_{\text{max}}) H + R_C \left( \sum_{i=1}^H |X(A_i)| + \sum_{i=1}^H |Y(A_i)| \right) + R_\alpha \sum_{i=1}^H \sum_{i=1}^H \alpha(A_i, A_i),$$

где  $R_H$ ,  $R_X$ ,  $R_Y$ ,  $R_W$ ,  $R_C$ ,  $R_\alpha$  — соответственно аппаратные сложности логического контроллера в составе ЛМК, портов ввода/вывода в составе логических контроллеров для приема сигналов логических условий и выдачи сигналов микроопераций, памяти микропрограмм в составе контроллера, подсистемы передачи сигналов логических условий/микроопераций и коммуникационной подсистемы для реализации команд межконтроллерной передачи управления,  $X_{\max}$  и  $Y_{\max}$  — соответственно число выводов контроллера для приема сигналов логических условий и выдачи сигналов микроопераций,  $W_{\max}$  — емкость памяти микропрограмм контроллера,  $\left|X\left(A_i\right)\right|$  — число сигналов логических условий, принимаемых условными вершинами i-го блока разбиения,  $\left|Y\left(A_i\right)\right|$  — число сигналов микроопераций, выдаваемых операторными вершинами i-го блока разбиения,  $\alpha\left(A_i,A_j\right)$  — число связей по управлению (микрокоманд передачи управления) между i-м и j-м блоками разбиения.

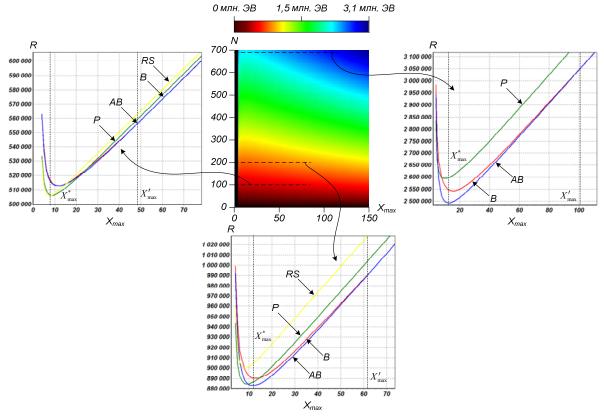

В ходе анализа качества разбиений, выполненного по результатам расчетов в проекте добровольных распределенных вычислений Gerasim@Home, было установлено наличие т.н. зон нечувствительности, в каждой из которых ослабление значений технологических ограничений выше некоторого порогового значения ( $X'_{\rm max}$ ,  $Y'_{\rm max}$  и  $W'_{\rm max}$ ) ведет лишь к увеличению аппаратной сложности ЛМК и не приводит к улучшению остальных показателей качества разбиений и соответствующих им технических характеристик ЛМК. Также было показано, что ценой незначительного 5%-го ухудшения значений частных показателей качества разбиений можно существенно (до 17,2 раз) сократить требования к числу выводов для приема/выдачи сигналов логических условий и микроопераций, однако влияние данной оптимизации на общую аппаратную сложность ЛМК ранее проанализировано не было. С целью исследования потенциала для снижения аппаратной сложности ЛМК в целом на основании полученных ранее экспериментальных данных был произведен расчет аппаратной сложности R в зависимости от числа вершин N = |A| в составе граф-схем алгоритмов управления, значений технологических ограничений на примере ограничения  $X_{\rm max}$  и анализа усредненных значений показателей

качества разбиений, результаты которого приведены на рис. 1, а оценки получаемого выигрыша в аппаратной сложности – в табл. 1.

Рис. 1. Зависимость аппаратной сложности R проектируемого ЛМК от числа вершин N в графсхемах алгоритмов управления и числа принимаемых контроллером сигналов логических условий  $X_{\max}$  при  $Y_{\max} = 100$  и  $W_{\max} = 100$  (В – сокращенное обозначение метода С.И. Баранова, АВ – жадного метода с ограничением на смежность, P – метода параллельнопоследовательной декомпозиции, RS – метода случайного перебора)

Таблица 1. Результаты оценки выигрыша в аппаратной сложности ЛМК

| N   | Граница области нечувстви- тельности $X'_{ m max}$ | Аппаратная сложность <i>R'</i> ЛМК на границе области нечувствительности | Оптима-<br>льное<br>значение<br>ограни-<br>чения<br>$X_{\max}^*$ | Аппаратная сложность $R^*$ ЛМК при оптимальном значении ограничения | Выи-<br>грыш $\eta = \frac{R'}{R^*}$ |

|-----|----------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------|

| 100 | 49                                                 | 556 – 565 тыс. ЭВ                                                        | 8                                                                | 508 – 516 тыс. ЭВ                                                   | 8-11%                                |

| 200 | 64                                                 | 995 – 1035 тыс. ЭВ                                                       | 8 – 15                                                           | 885 – 900 тыс. ЭВ                                                   | 12-17%                               |

| 700 | 101                                                | 3,05 – 3,15 млн. ЭВ                                                      | 9 – 16                                                           | 2,49 – 2,59 млн. ЭВ                                                 | 18-27%                               |

В ходе анализа полученных результатов можно сделать вывод о том, что выбор оптимального значения  $X_{\rm max}^*$  числа выводов для приема логических сигналов от объекта управления позволяет снизить аппаратную сложность проектируемого ЛМК от 8% до 27% в зависимости от размера граф-схем алгоритмов управления. При этом вклад в данную величину выбора оптимального метода синтеза разбиений составляет от 1,5% до 4%.

## Литература

1. Ватутин Э.И. Проектирование логических мультиконтроллеров. Синтез разбиений параллельных граф-схем алгоритмов. Saarbrucken: Lambert Academic Publishing, 2011 г. 292 с.